## Lecture Notes in Computer Science

3688

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Rune Winther Bjørn Axel Gran Gustav Dahll (Eds.)

# Computer Safety, Reliability, and Security

24th International Conference, SAFECOMP 2005 Fredrikstad, Norway, September 28-30, 2005 Proceedings

#### Volume Editors

Rune Winther Østfold University College Faculty of Computer Sciences 1757 Halden, Norway E-mail: rune.winther@hiof.no

Bjørn Axel Gran Gustav Dahll Institute for Energy Technology Software Engineering Laboratory 1761 Halden, Norway E-mail: bjorn.axel.gran@hrp.no; g.dahll@halden.net

Library of Congress Control Number: 2005932842

CR Subject Classification (1998): D.1-4, E.4, C.3, F.3, K.6.5

ISSN 0302-9743

ISBN-10 3-540-29200-4 Springer Berlin Heidelberg New York ISBN-13 978-3-540-29200-5 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11563228 06/3142 5 4 3 2 1 0

## Preface

Welcome to SAFECOMP 2005, held in Fredrikstad, Norway. Since its establishment SAFECOMP, the series of conferences on Computer Safety, Reliability and Security, has contributed to the progress of the state of the art in dependable applications of computer systems. SAFECOMP provides ample opportunity to exchange insights and experiences in emerging methods and practical experience across the borders of different disciplines. Previous SAFECOMPs have year after year registered new multidisciplinary trends on dependability of computer-based systems.

SAFECOMP 2005 focused on dependability of critical computer applications and was a platform for knowledge and technology transfer between academia, industry and research institutions. Papers were invited on all aspects of dependability and survivability of critical computer-based systems in various branches and infrastructures. Due to the increasing awareness and importance of security issues of critical computer-based systems, SAFECOMP 2005 emphasized work in this area. Nowadays practical experience points out the need for multidisciplinary approaches to deal with the nature of critical complex settings.

The SAFECOMP 2005 program consisted of 30 papers selected from 84 submissions. The 30 papers represented scientists from 14 different countries acknowledging the world-wide interest of SAFECOMP and the addressed topics. The SAFECOMP program was supplemented by keynote talks enhancing the technical and scientific merit of the conference, a number of co-located activities, meetings and tutorials, and a technical visit to the research environment in Halden which organized the conference.

We would like to thank the International Program Committee, the external reviewers, the keynote speakers, and the authors for their work in support of SAFECOMP 2005. We would also like to thank the conference staff at the Institute of Energy Technology and Østfold University College. We really enjoyed the work, and we hope you appreciated the care we put into organizing the conference. Finally, we would like to extend to you the invitation to attend and contribute to SAFECOMP 2006 in Gdansk, Poland (www.safecomp.org).

July 2005

Gustav Dahll Bjørn Axel Gran Rune Winther

## Organization

## SAFECOMP 2005 Organization

#### General Chair

Gustav Dahll, Norway

#### **Program Co-chairs**

Bjørn Axel Gran, Norway Rune Winther, Norway

#### **EWICS Chair**

Udo Voges, Germany

#### Organizing Committee

Rune Fredriksen, Norway Siv-Hilde Houmb, Norway Monica Kristiansen, Norway John Petter Kvalvik, Norway Jørn L. Pettersen, Norway Atoosa P.-J. Thunem, Norway Bjørn Axel Gran, Norway Rune Winther, Norway

### **International Program Committee**

Stuart Anderson, UK Terje Aven, Norway Ramesh Bharadwaj, USA Robin Bloomfield, UK Sandro Bologna, Italy Andrea Bondavalli, Italy Inga-Lill Bratteby-Ribbing, Sweden Bettina Buth, Germany Stefan Christiernin, Sweden Gustav Dahll, Norway Peter Daniel, UK Massimo Felici, UK Robert Genser, Austria Chris Goring, UK Januscz Gorski, Poland Bjorn Axel Gran, Norway Wolfgang Grieskamp, USA Wolfgang Halang, Germany Kai Hansen, Norway Monika Heiner, Germany Maritta Heisel, Germany Connie Heitmeyer, USA Atte Helminen, Finland Peter Jacobsson, Sweden Ole-Arnt Johnsen, Norway Chris Johnson, UK Erland E. Jonsson, Sweden Mohamed Kaâniche, France Karama Kanoun, France Martin Kropic, Czech Republic Kenneth Kvinnesland, Norway Dennis Kügler, Germany

Peter B. Ladkin, Germany Peter Liggesmeyer, Germany Oliver Mäckel, Germany Meine van der Meulen, UK Odd Nordland, Norway Jan G. Nordstrøm, Norway Alberto Pasquini, Italy Gerd Rabe, Germany Felix Redmill, UK Judith Rossebø, Norway Martin Rothfelder, Germany Francesca Saglietti, Germany Erwin Schoitsch, Austria Terje Sivertsen, Norway Jeanine Souquières, France Werner Stephan, Germany Ketil Stølen, Norway Tor Stålhane, Norway Asuman Suenbuel, USA Mark Sujan, UK Thomas Santen, Germany Atoosa P.-J. Thunem, Norway Jos Trienekens, The Netherlands Adolfo Villafiorita, Italy Udo Voges, Germany Albrecht Weinert, Germany Marc Wilikens, Italy Rune Winther, Norway Stefan Wittmann, Germany Eric Wong, USA Zdzislaw Zurakowski, Poland

#### External Reviewers

Matthias Anlauff Terje Andersen Lassaad Cheikhrouhou Silvano Chiaradonna Felicita Di Giandomenico Lorenzo Falai Siv-Hilde Houmb Martin Gilje Jaatun

Terje Jensen Tor Hjalmar Johannessen Luca Save Mass Soldal Lund Tom Lysemose Andreas Nonnengart Simone Pozzi Yu Qi Atle Refsdal

Georg Rock Fredrik Seehusen Nikolai Tillmann Inger Anne Tøndel Fredrik Vraalsen Linzhang Wang

### **Sponsoring Organizations**

#### Scientific Sponsor

#### Scientific Co-sponsors

## seibersdorf research

An enterprise of the Austrian Research Centers.

COMPUTER SOCIETY

IFIP WG10.4 on Dependable Computing and Fault Tolerance IFIP WG13.5 on Human Error, Safety and System Development

European Network of

Halden IT Forum

Clubs for SCSC - Safety-Critical Systems Club

REliability and SRMC - Software Reliability & Metrics Club

Safety of NONSTOPP - NOrsk Nettverk for Sikre Trygge Og Pålitelige

Software Programmerbare Systemer

## **Table of Contents**

| CMMI RAMS Extension Based on CENELEC Railway Standard  Jose Antonio Fonseca, Jorge Rady de Almeida Júnior                                                                                                    | 1   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| The Importance of Single-Source Engineering of Emergency and Process Shutdown Systems  *Robert Martinez, Torgeir Enkerud                                                                                     | 13  |

| Combining Extended UML Models and Formal Methods to Analyze Real-Time Systems  Nawal Addouche, Christian Antoine, Jacky Montmain                                                                             | 24  |

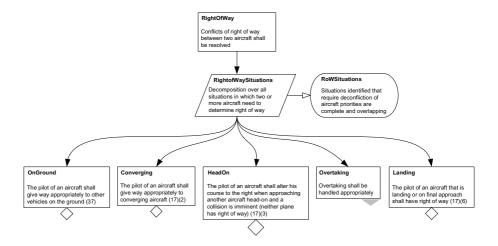

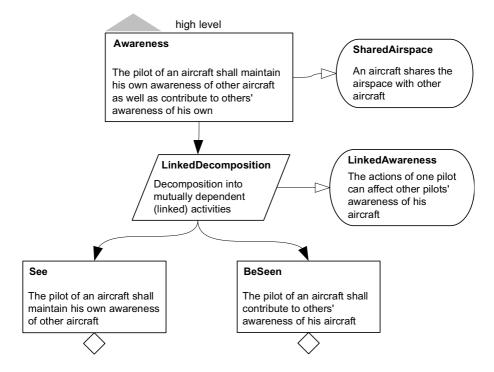

| Defining and Decomposing Safety Policy for Systems of Systems  Martin Hall-May, Tim P. Kelly                                                                                                                 | 37  |

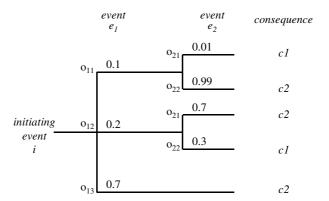

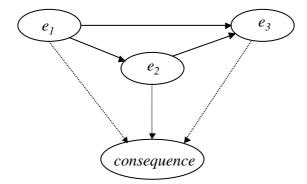

| Generalising Event Trees Using Bayesian Networks with a Case Study of Train Derailment  George Bearfield, William Marsh                                                                                      | 52  |

| Control and Data Flow Testing on Function Block Diagrams  Eunkyoung Jee, Junbeom Yoo, Sungdeok Cha                                                                                                           | 67  |

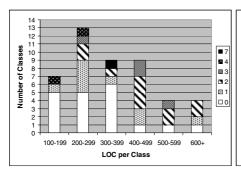

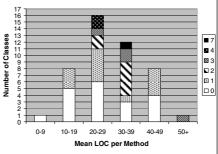

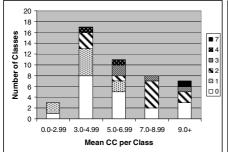

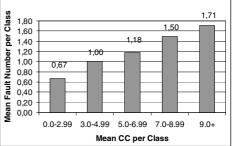

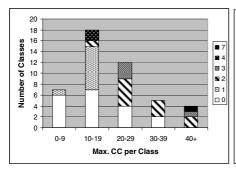

| Comparing Software Measures with Fault Counts Derived from Unit-Testing of Safety-Critical Software  Wolfgang Herzner, Stephan Ramberger, Thomas Länger, Christian Reumann, Thomas Gruber, Christian Sejkora | 81  |

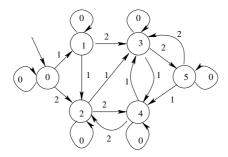

| Automatic Analysis of a Safety Critical Tele Control System  Edoardo Campagnano, Ester Ciancamerla, Michele Minichino,  Enrico Tronci                                                                        | 94  |

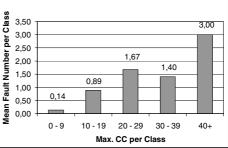

| A Formal Model for Fault-Tolerance in Distributed Systems  Brahim Hamid, Mohamed Mosbah                                                                                                                      | 108 |

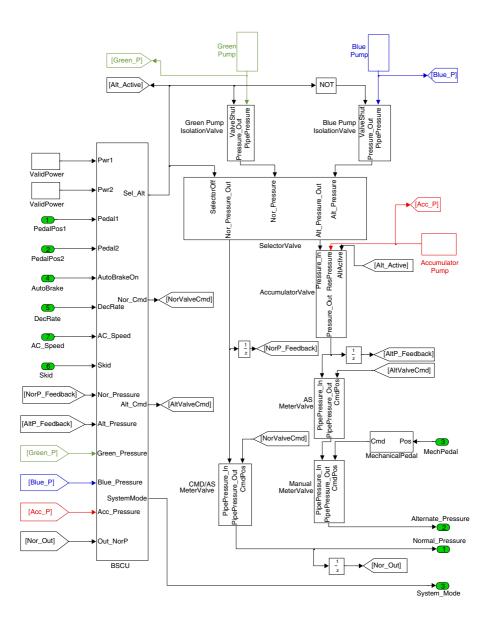

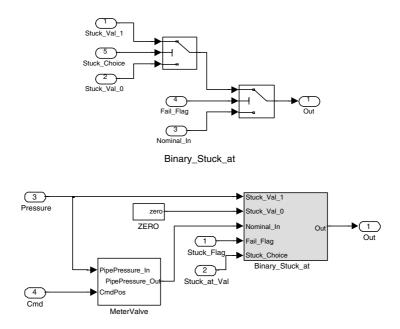

| Model-Based Safety Analysis of Simulink Models Using SCADE Design Verifier  Anjali Joshi, Mats P.E. Heimdahl                                                                                                 | 122 |

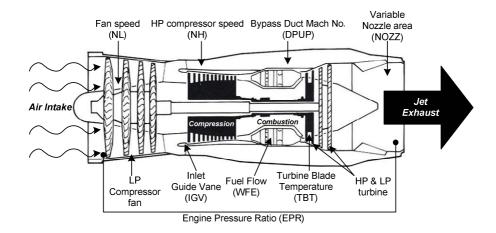

| Using Safety Critical Artificial Neural Networks in Gas Turbine Aero-Engine Control Zeshan Kurd, Tim P. Kelly                                                                                                | 136 |

#### XII Table of Contents

| On the Effectiveness of Run-Time Checks  Meine J.P. van der Meulen, Lorenzo Strigini, Miguel A. Revilla                                | 151 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Technique for Fault Tolerance Assessment of COTS Based Systems  Ruben Alexandersson, D. Krishna Chaitanya, Peter Öhman,  Yasir Siraj | 165 |

| Finding Upper Bounds for Software Failure Probabilities – Experiments and Results  Monica Kristiansen                                  | 179 |

| Justification of Smart Sensors for Nuclear Applications  Peter Bishop, Robin Bloomfield, Sofia Guerra, Kostas Tourlas                  | 194 |

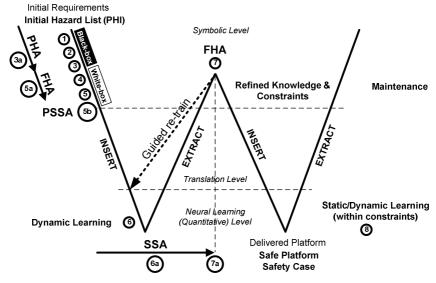

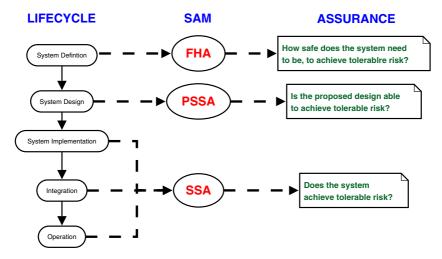

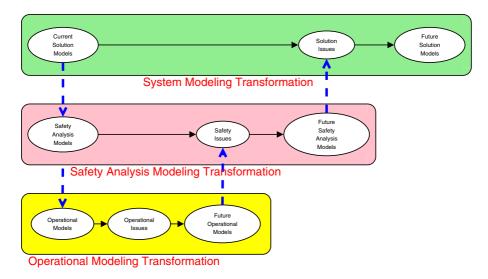

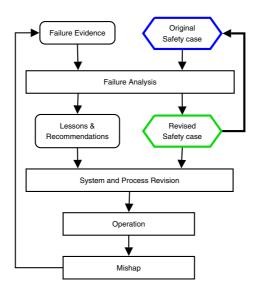

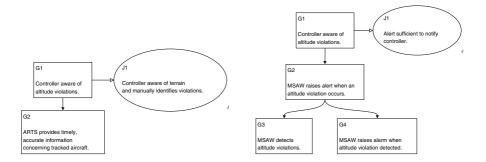

| Evolutionary Safety Analysis: Motivations from the Air Traffic Management Domain  Massimo Felici                                       | 208 |

| Public-Key Cryptography and Availability  Tage Stabell-Kulø, Simone Lupetti                                                            | 222 |

| End-To-End Worst-Case Response Time Analysis for Hard Real-Time Distributed Systems  Lei Wang, Mingde Zhao, Zengwei Zheng, Zhaohui Wu  | 233 |

| Safety Interfaces for Component-Based Systems  Jonas Elmqvist, Simin Nadjm-Tehrani, Marius Minea                                       | 246 |

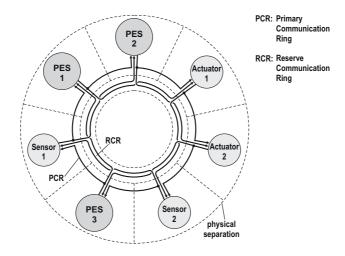

| A Safety-Related PES for Task-Oriented Real-Time Execution Without Asynchronous Interrupts  Martin Skambraks                           | 261 |

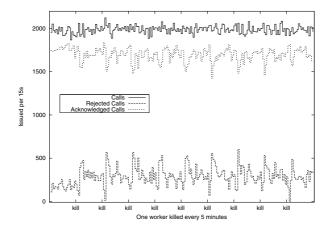

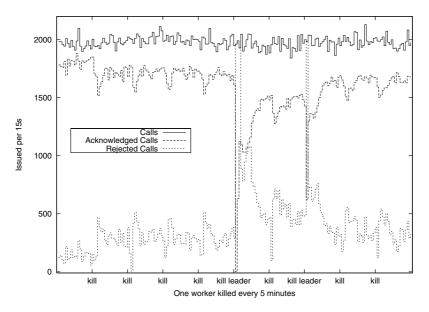

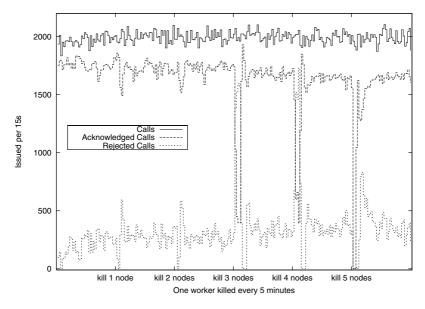

| Are High-Level Languages Suitable for Robust Telecoms Software?  J.H. Nyström, P.W. Trinder, D.J. King                                 | 275 |

| Functional Apportioning of Safety Requirements on Railway Signalling<br>Systems                                                        |     |

| Ola Løkberg, Øystein Skogstad                                                                                                          | 289 |

| Automatic Code Generation for PLC Controllers  Krzysztof Sacha                                                                         | 303 |

| The TACO Approach for Traceability and Communication of<br>Requirements                                |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Terje Sivertsen, Rune Fredriksen, Atoosa P-J Thunem,<br>Jan-Erik Holmberg, Janne Valkonen, Olli Ventä, |     |

| Jan-Ove Andersson                                                                                      | 317 |

| An IEC 62061 Compliant Safety System Design Method for Machinery Bengt Ljungquist, Thomas Thelin       | 330 |

| Design Evaluation: Estimating Multiple Critical Performance and Cost Impacts of Designs  Tom Gilb      | 344 |

| The Application of an Object-Oriented Method in Information System<br>Security Evaluation              |     |

| Qiang Yan, Hua-ying Shu                                                                                | 357 |

| Towards a Cyber Security Reporting System – A Quality Improvement<br>Process                           |     |

| Jose J. Gonzalez                                                                                       | 368 |

| Security Research from a Multi-disciplinary and Multi-sectoral<br>Perspective                          |     |

| Atoosa P-J Thunem                                                                                      | 381 |

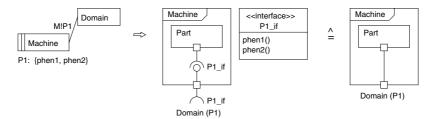

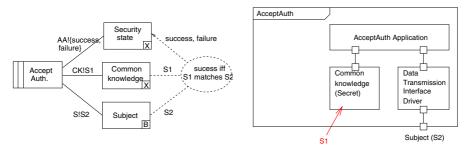

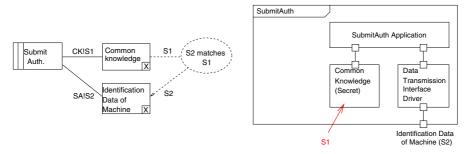

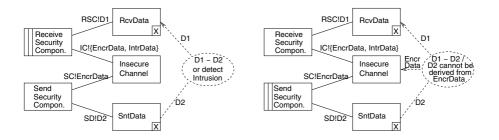

| Problem Frames and Architectures for Security Problems  Denis Hatebur, Maritta Heisel                  | 390 |

| Author Index                                                                                           | 405 |

## CMMI RAMS Extension Based on CENELEC Railway Standard

Jose Antonio Fonseca and Jorge Rady de Almeida Júnior

Computational and Digital Systems Engineering Department, Polytechnic School, University of São Paulo, Brazil

Abstract. Railway systems are also dependable systems and, considering their importance, it is vital to assure the application of adequate design techniques. So, this work presents a RAMS (Reliability, Availability, Maintainability and Safety) extension for CMMI SE-SW version 1.1 "Capability Maturity Model® Integration" developed by SEI (Software Engineering Institute), based on CENELEC 50126, 50128 and 50129 standards developed to normalize RAMS aspects of railway control systems in European Community. This extension is based on the inclusion of four new Process Areas into the CMMI SE-SW, increasing its actual number from 22 to 26, without changes in the CMMI model basic structure. The objective of this extension is to obtain a support tool for design process applicable to enterprises that develop railway systems and are adopting CMMI or migrating from other CMM models.

#### 1 Introduction

This work represents an attempt to join two very important tendencies that are being verified by the maturity models use and the railway applications design. Considering the great capacity of CMM models to assist innumerous application areas, the first trend can be observed through an increase in the use of maturity models by industrial community. The focus of such models is represented by CMMI (Capability Maturity Model Integration). The second trend is composed by integration efforts to create a consensus about RAMS (Reliability, Availability, Maintainability and Safety) criteria for railways applications between the European Union members that is represented by CENELEC standards.

This work has also a very closely relationship with others efforts to incorporate new specifics aspects to CMMI, such as the job sponsored by FAA (Federal Aviation Administration) to include Safety and Security requirements in iCMM and CMMI and the task headed by Australian Government's Defense Material Organization (DMO) in the creation of +Safe, a safety extension to CMMI.

The section 2 presents a brief description about the CMMI model, while section 3 presents the mains aspects of the CENELEC Standards. Section 4 contains the proposed extension of RAMS extension for CMMI model. Finally, section 5 presents the mains conclusions of this paper.

#### 2 The CMMI Model

The extensive use of the SW-CMM [9] (Capability Maturity Model for Software) by the organizations promoted the creation of similar models to address other areas not directly related with software development. Considering such aspect, many other models have arisen to support production systems, subcontracting areas, etc. But, all of these models were not created in order to facilitate integration among them, generating problems with their simultaneous implementation in an organization.

This fact has revealed the need of creating an integrated model, aiming a uniform view, besides the elimination of existing redundancies among the various maturity models. We can say that the CMMI is a result of a great integration work, and that it was elaborated to allow a convergence of the main existing maturity models. The CMMI structure also allows integration of new areas, which reinforces its integration capacity.

The CMMI SE/SW (Capability Maturity Model for Systems and Software Engineering) model V1.1 [5] consists of 22 Process Areas. A Process Area is a group of related practices that, when accomplished together, means that a set of important objectives were achieved, obtaining a significant improvement in such area.

All the CMMI Process Areas are common to the stage representation and the continuous representation. In the <u>stage representation</u>, the Process Areas are organized through <u>maturity levels</u>. Considering one level, all of its Process Areas are in the same maturity level. In the <u>continuous representation</u>, the maturity of a Process Area is called <u>capability level</u> and each Process Area can be in any of the six capability levels existents, independently of any other Process Area.

Thus, the name "maturity level" refers to a pre-defined group of Process Areas, which are in the same maturity level, whereas "capability level" refers only to an individual Process Area.

The continuous representation allows that one organization can choose the more adequate improvement sequence to its business goals, making possible a reduction of the risk areas.

The stage representation also offers a series of improvements, starting from basic management practices and going through a predefined plan of successive levels where each level is the basis for the next one.

To completely satisfy a Process Area, both generic and specific goals must be accomplished. Specific goals are applied to a Process Area and refer to single characteristics, which describe what has to be done to satisfy a Process Area.

The <u>specific goals</u> are supported by specific practices which are activities considered important to achieve a specific goal. The specific practices describe the activities, which must be accomplished in order to reach a specific goal of a Process Area.

<u>Generic goals</u> are called "generic" because a single goal can appear in multiple Process Areas. Considering the staged representation, every Process Area has a single specific goal. Generic goals are supported by common practices.

The CMMI continuous representation allows one organization to keep its capacity on the improvement of a single Process Area, or on multiple specific Process Areas. Each Process Area has its own specific goals associated similarly to the staged representation. Each capability level (from 0 to 5) has a common goal and many common practices.

The staged representation does not have requirements for the first maturity level; whereas, in the continuous representation there are specific and generic goals to be accomplished in order to achieve capability level 1. This has increased the granularity of the capability (process maturity), in such way that the organizations show early progress. This can be important in organizations that are under pressure to present immediate results.

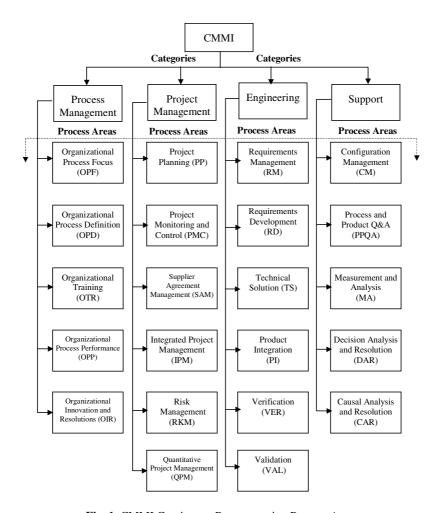

The 22 Process Areas are divided into four categories, according to figure 1. In the activity of selecting a Process Area or a single category, an organization can focus its improvement efforts in such area. Each one of the 22 Process Areas can be characterized individually by the CMMI as having a maturity level from 0 through 5, as follows:

#### Capability Level 0 - Incomplete

An incomplete process is a partially accomplished or a non-accomplished process, that is, at least one of the specific goals of the Process Area is not achieved.

#### Capability Level 1 – Executed

At this level, processes achieve the specific goals of the correspondent Process Area. The process supports the necessary work to generate the required products from the inputs, which are correctly identified during the process. The difference between an incomplete process and an executed process is that an executed process achieves all the specific goals of the Process Area.

#### Capability Level 2 – Managed

A managed process consists in an executed process (capacity level 1), which is also planned and executed, according to a plan, which embraces qualified people, adequate resources and appropriate participants. The process is monitored, controlled, revised and evaluated according to its process description adherence and it can be instantiated to a design, group or organizational function. The process management comprises the Process Area institutionalization and the accomplishment of other specific objectives defined for the process, such as cost, time schedule and quality goals.

#### Capability Level 3 – Defined

A defined process is a managed process (capacity level 2), which includes a group of default processes according to the organization objectives, its metrics, and other information on process improvement.

#### Capability Level 4 – Quantitatively Managed

A quantitatively managed process is a defined process (capacity level 3), which is controlled through the use of statistics and other quantitative techniques. The quantitative objectives of quality and process performance are established and used as a criterion in the process management. The quality and process performance are transformed into statistics expressions and managed through the process lifecycle.

#### Capability Level 5 – Optimized

An optimized process is a quantitatively managed process (capacity level 4), which is modified and adapted to achieve the business and relevant goals in a specific moment. An optimized process is focused on the continuous improvement of the process performance through the use of technological improvement and innovative technologies.

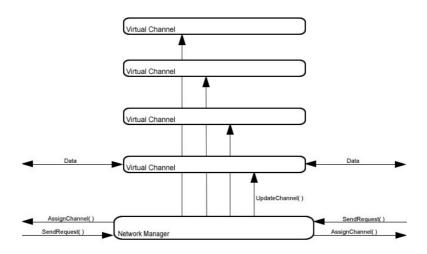

Fig. 1. CMMI Continuous Representation Process Areas

#### 3 The CENELEC Standards

Since the first steps towards a single market of railway transport services in the European Union, it became evident the existence of different regulations in the safety issue.

The main reason for this situation can be explained by the fact that local national operators, which have all the responsibility for the systems operation inside their territories, perform the railway transport management of these countries. However, considering the increasingly integration of the European railway systems, the safety aspect should be considered in the most general ambit of the European Union [1].

At present, the railway industry is observing a process of developing appropriate safety standards that can control the new devices created by the technology development, seeking to ensure the adequate safety level for the systems. Railway suppliers are looking for standards that can aid them to show evidences about the safety of their products. Railway owner/operators are also insecure about what they can expect from suppliers, in order to make them feel more comfortable in accepting a product [6], [7].

The European Union, through the European Committee for Electrotechnical Standardization (CENELEC), has been developing standards for the safety issues regulation for railway application [1]. All the European Union members desire to turn possible the interoperability among the several existing systems, through the adoption of such standards.

The main focus of the CENELEC standards is composed by a systematic hazard identification followed by a risk reduction at an acceptable level. Considering the necessary risk reduction, CENELEC standards "recommend" techniques and methods that permit to demonstrate that the required RAMS targets levels are satisfied.

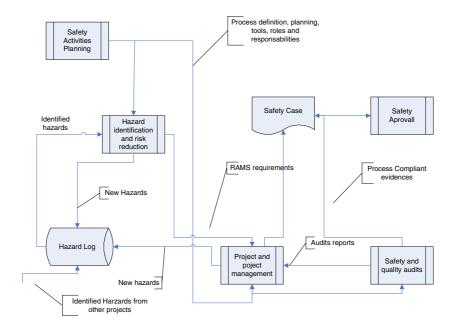

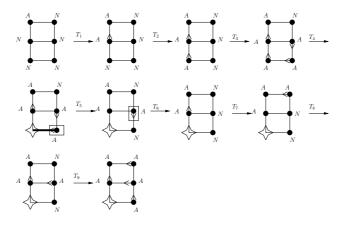

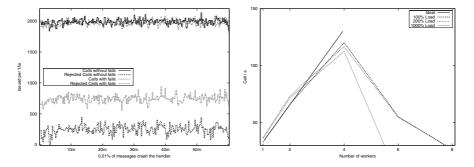

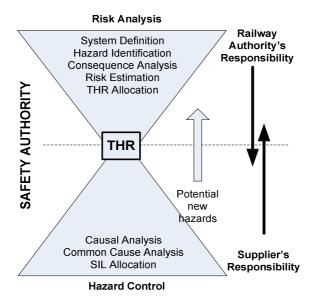

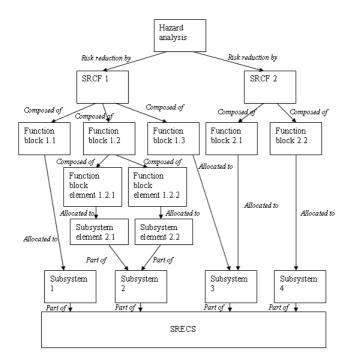

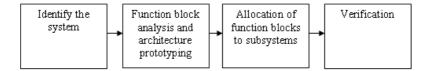

CENELEC standards consider the critical systems design according to the focus shown in the figure 2. Some of the activities presented in that figure are described in a simplified way.

The philosophy adopted by CENELEC Standards is based in systematic hazard identification [8]. For each identified hazard there must be, at least, one requirement to eliminate or mitigate the risk associated to that hazard.

Since the initial railway design phases, all RAMS related activities are made in agreement with CENELEC standards, considering also the SIL (Safety Integrity Level) required for the application, as defined by the operator [6] or by the supplier, according to a National Safety Regulatory Office. This phase product is a Safety Plan report that defines all design activities, including audits, responsibilities, roles and design schedules.

The Hazard Identification and risk reduction are activities performed during all the design lifecycle. In early phases, it is made a Preliminary Hazard Analyses (PHA), whose objective is to define a basic set of safety requirements that must be detailed in posterior phases. This activity must consider the Hazard Log contents. This Hazard Log is constantly updated along the system design development with new identified hazards.

The requirements identified in previous phases are refined in the design phase, where the solutions needed to satisfy the identified requirements are developed. The CENELEC Standards describes the main activities needed to demonstrate that the RAMS principles were correctly applied during each development phase, always considering the selected SIL [2], [3], [4].

For CENELEC, the SIL define the depth which the design should be analyzed, the necessary evidences to demonstrate that all specified requirements are satisfied and define the hierarchical constrains and the required personal skills to the design development.

Audits are performed during system development, whose function is to verify the compliance with directives contained in Plans for Quality Assurance, for Configuration Management, for Safety and others. A report is generated for each audit aspect, in order to demonstrate the design status.

Fig. 2. CENELEC Basic Process

The set of evidences collected during system development and design deliverables are used to elaborate a Safety Case, also known as Technical Safety Report (TSR). A TSR is a dossier that demonstrates that RAMS requirements were correctly captured, satisfied and traceable.

#### 4 The RAMS Extension for CMMI

As previously mentioned, both CMMI model and CENELEC standards propose concept unification in their application areas. But, organizations that are developing safety-critical systems need to consider the concepts established in those two frameworks in an integrated way, which is very difficult, considering that the their structures does not consider such kind of integration.

The main problem in using both CMMI and CENELEC in the same application is that CMMI does not attend the RAMS aspects. This fact makes necessary to apply another specific standard, in order to supply such RAMS aspects. However, CENELEC does not provide, itself, an evaluation system and a guide to its implementation, like CMMI. On the other hand, the simultaneous application of the CMMI and CENELEC standards, in a separate way, without a previous harmonization, can generate problems such overlaps, different interpretations and misunderstandings.

Thus, the proposal of this work is to make the unification of these two frameworks into a single structure, flexible enough to support the necessary adaptations.

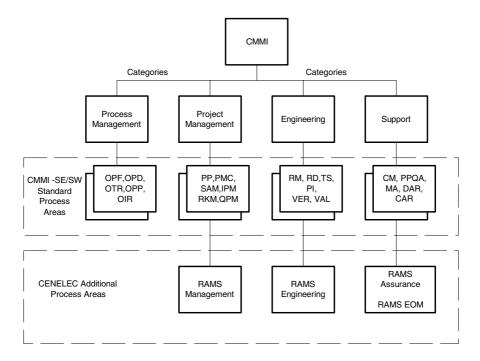

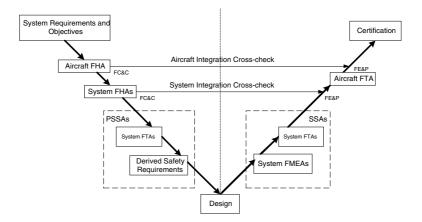

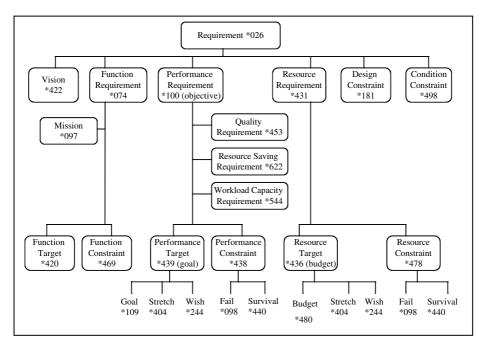

Fig. 3. RAMS Extension Structure

This paper proposes the addition of RAMS into the CMMI structure, without modifying its fundamental structure, which is widely accepted. So, the CENELEC standard arrangement is modified to attend the CMMI language. If we have tried the inverse solution, that is, incorporate CMMI into CENELEC standards, there would be a problem related to the great quantity of practices to be inserted into the CENELEC standards, in order to cover all the CMMI aspects. This happens because CENELEC standards are specific in their area and CMMI is a common model for systems. A second problem would be the generation of unnecessary redundancies and the need of generating a mapping between the model and the standard.

We believe that the introduction of the CENELEC concepts into CMMI will be more natural for the most organizations, reducing implementation costs and time, when considering the application of these concepts in a separate way.

Primarily the RAMS extension was implemented in CMMI SE-SW continuous representation (presented in figure 1), because we believe that continuous representation provide the necessary flexibility according to organizations needs, schedules and budget, although staged representation can also be used.

To satisfy CENELEC Standards, besides the inclusion of new RAMS Process Areas, it is necessary to implement the existent areas of CMMI. Note that these Process Areas are distributed in levels 2 and 3 of the staged representation. Therefore it is necessary to implement the level 3 for these representations to satisfy CENELEC standards. In

addition, some Process Areas of CMMI, above mentioned, exceed CENELEC requirements, but this fact contribute with CENELEC process improvement.

The new Process Areas are included in CMMI SE-SW continuous representation as show in figure 3. As shown, the four new Process Areas are distributed between three CMMI categories, as follow:

CMMI Category

Process Areas

Project Management

RAMS Management

Engineering

RAMS Engineering

Support

RAMS Assurance

RAMS Environment Organization and Maintenance

Table 1. New Process Areas

The main objectives of the new Process Areas and their respective Specific Goals (SG) are:

#### **RAMS Management**

#### **Purpose**

The aim of this Process Area is to monitor the product development process, checking if the RAMS activities are performed as planned and tracking the design evolution.

#### Related Process Areas

There are many processes areas related with RAMS Management. These areas and their respective connections with RAMS Management are:

- Requirements Development: acquisition of information about developing requirements that define the product and product components;

- Requirements Management: acquisition of information about managing requirements needed for planning and re-planning;

- Technical Solution: acquisition of information about transforming requirements into product and product component solutions;

- Organizational Process Definition: acquisition of information about the design lifecycle and basic guidelines; and

- RAMS Environment Organization and Maintenance: identification of organization requirements, knowledge and skills.

#### **Practice-to-Goal Relationship Table**

#### SG 1. Develop a RAMS Plan

- SP1.1-1 Establish Validation Strategy

- SP1.2-1 Establish RAMS Organization, Roles and Responsibilities

- SP1.3-1 Establish RAMS Lifecycle to the Design

- SP1.4-1 Establish Audits and Assessments Points

- SP1.5-1 Plan for Data Management

- SP1.6-1 Plan for Resources

- SP1.7-1 Plan for Needed Knowledge and Skills

- SP1.8-1 Plan Stakeholder Involvement

- SP1.9-1 Plan Safety Reviews

- SP1.10-1Establish the RAMS Plan

#### SG 2. Obtain Commitment to the Plans

- SP 2.1-1 Review Plans that Affect the Design

- SP 2.2-1 Reconcile Work and Resource Levels

- SP 2.3-1 Obtain Plans Commitments

#### SG 3. Develop an Installation and Commissioning Plan

- SP3.1-1 Establish Installation and Commissioning Strategy

- SP3.2-1 Establish Roles and Responsibilities

- SP3.3.1 Plan for Resources

- SP3.4.1 Plan for Needed Knowledge and Skills

- SP3.5.1 Plan Stakeholder Involvement

- SP3.6.1 Establish the RAMS Plan

#### SG 4. Monitor Safety Incidents

SP4.1-1 Monitor Safety Incidents

#### **RAMS Engineering**

#### **Purpose**

The aim of the RAMS Engineering is to define the activities that must be performed, in order to assure that the generated products have the desired and adequate RAMS levels for the application.

#### **Related Process Areas**

There are many processes areas related with RAMS Engineering. These areas and their respective connection with RAMS Engineering are:

- Requirements Development: decision on how to allocate or distribute requirements among the product components;

- Technical Solution: acquisition of more information about RAMS decisions;

- Project Planning: how design plans reflect requirements and need to be revised with changes in requirements;

- Configuration Management: obtain information about baselines and controlling changes, considering configuration issues;

- Project Monitoring and Control: activities track and control, taking appropriate corrective actions; and

- Requirements Management: get information about managing requirements.

#### **Practice-to-Goal Relationship Table**

#### SG 1. Identify Safety Requirements

- SP1.1-1 Perform Hazard Analysis

- SP1.2-1 Perform Risk Assessment

- SP1.3.1 Define Risk Tolerance Criteria

#### SG 2. Develop Safety Requirements

- SP2.1-1 Allocate Safety Requirements to Products

- SP2.2-1 Apply Safety Principles to Safety Requirements

- SP2.3-1 Justify Technical Safety Decisions

#### SG 3. Establish a Hazard Log

SP3.1-1 Establish a Hazard Log to the Design

#### SG 4. Identify RAM requirements

- SP4.1-1 Perform Preliminary RAM Analysis

- SP4.2-1 Identify External Influence over RAM Requirements

#### **SG 5. Develop RAM Requirements**

- SP5.1-1 Allocate RAM Requirements to Products

- SP5.2-1 Justify Technical RAM Decisions

#### SG 6. Demonstrate the Safety of the system

- SP6.1-1 Perform Analysis about Effects of Faults

- SP6.2-1 Perform Analysis about External Influences

- SP6.3-1 Perform Analysis about Application Conditions

- SP6.4-1 Perform Safety Qualification Tests

- SP6.5-1 Develop a Technical Safety Report

#### **RAMS Assurance**

#### **Purpose**

The aim of the RAMS Assurance is to evaluate, continuously, the correct accomplishment of design lifecycle activities and the related RAMS products, which are generated by engineering activities, in order to assure the product integrity.

#### **Related Process Areas**

There are many processes areas related with RAMS Assurance. These areas and their respective connection with RAMS Assurance are:

- Project Planning: identification of the processes and the associated products that need to be evaluated;

- Verification: satisfaction of RAMS requirements;

- Process and Product Quality Assurance: audits on RAMS process and evidences:

- RAMS Management: acquisition of safety management evidences

- RAMS Engineering: acquisition of evidences about functional/technical safety

- RAMS Environment Organization and Maintenance: identification of knowledge and skills.

#### **Practice-to-Goal Relationship Table**

#### SG 1. Develop an Assessment Plan

- SP1.1-1 Establish Assessment Strategy

- SP1.2-1 Establish Roles and Responsibilities

- SP1.3-1 Plan for Resources

- SP1.4-1 Plan for Needed Knowledge and Skills

- SP1.5-1 Plan Stakeholder Involvement

- SP1.6-1 Identify Design, Personnel or Documents Dependencies

- SP1.7-1 Establish the Assessment Plan

#### SG 2. Perform evaluations

- SP2.1-1 Perform Interviews with Design Personnel

- SP2.2-1 Perform Examination of Design Documents

- SP2.3-1 Perform Observation of Practices, Design Activities and Conditions

- SP2.4-1 Re-work of Parts of the Safety Analysis if Necessary

- SP2.5.1Demonstrations Arranged at the Assessor's Request

- SP2.6.1Elaborate an Assessment Report

#### SG 3. Develop a Safety Case

- SP3.1-1 Collect evidences of Quality Management

- SP3.2-1 Collect Evidences of Safety Management

- SP3.3-1 Collect Evidences about Functional/Technical Safety

- SP3.4-1 Develop a Safety Case

#### **RAMS Environment Organization and Maintenance**

#### **Purpose**

The aim of the RAMS Environment Organization and Maintenance is to create a suitable infrastructure to support RAMS activities, select RAMS specialists, and define roles and responsibilities.

#### **Related Process Areas**

The Process Area related with RAMS Environment and Maintenance is the Organizational Training that can be consulted for information about how to creates skills.

#### **Practice-to-Goal Relationship Table**

#### SG 1. Establish environment and organization to RAMS Activities

- SP1.2-1 Identify Overall RAMS Organization

- SP1.1-1 Identify and Create Necessary Skills

- SP1.3-1 Define Roles and Responsibilities

- SP1.4-1 Identify Necessary Independence for Activities

- SP1.5-1 Maintain the Qualification of Environment Components

- SP1.5-1 Plan for Continuity and Improvements

#### **Final Remarks**

To provide CMMI compatibility with CENELEC standard, some CMMI Process Areas need modifications. For Verification and Validation Process Areas, it is

necessary to formalize Verification and Validation Plans and for the Organizational Process Definition Process Area it is necessary to adopt CENELEC lifecycle descriptions for software and system development.

#### 5 Conclusions

This paper presented an extension for CMMI based on the CENELEC standards, having the objective of aiding organizations that develop railway systems to work in an integrated way with CMMI and CENELEC standards, enabling reduction of time and its associated costs, when compared with an implementation using those two frameworks in an isolated way.

After a careful refinement process, we believe that this work could come to be very useful to the railway applications.

However, this extension does not include all the details of CENELEC standards because it does not define, specifically, as the activities should be done. These details should be defined for the organizations in accordance with the design needs of the based on CENELEC.

In that way, the basic structure of the proposed extension is generic and could be applied to other areas just needing the inclusion of the specific practices of that new area.

In future works it will be detailed the specific practices for each specific objective and will be analyzed the compatibility between Process Areas of this work and other works such as +Safe and FAA-iCMM.

#### References

- 1. CEC DIRECTIVE OF THE EUROPEAN PARLIAMENT AND OF THE COUNCIL, Commission of the European Communities, Brussels, 2002.

- CENELEC126- COMITÉ EUROPÉEN DE NORMALISATION ÉLECTROTECHNIQUE. Railway applications: The specification and Demonstration of Reliability, Availability, Maintainability and Safety – BS EN50126. Brussels, CENELEC, 1999.

- 3. CENELEC128- COMITÉ EUROPÉEN DE NORMALISATION ÉLECTROTECHNIQUE. Railway applications: Software for railways control and protection systems BS EN50128. Brussels, CENELEC, 2001.

- CENELEC129- COMITÉ EUROPÉEN DE NORMALISATION ÉLECTROTECHNIQUE. Railway applications: Safety related electronic system for Signalling – BS EN50128. Brussels, CENELEC, 2003.

- CMMI SE-SW- The Capability Maturity Model Integration, ver. 1.1, December 2001 Software Engineering Institute.

- McNICOL M. "Signalling systems, a view to the future". Railsafe 99 26-27 jully, 1999 Sydney, Australy

- 7. NERA Safety Regulation and Standards for European Railways February 2000, London.

- 8. SCHABE H. "The Safety Philosophy behind the CENELEC Railways Standards", 2002.

- 9. SW-CMM Capability Maturity Model for Software, version 2.0,1997, software Engineering Institute.

## The Importance of Single-Source Engineering of Emergency and Process Shutdown Systems

Robert Martinez and Torgeir Enkerud

ABB AS, Corporate Research Center, Bergerveien 12, PO Box 90, NO-1375 Billingstad, Norway robert.martinez@no.abb.com, torgeir.enkerud@no.abb.com

**Abstract.** Emergency/Process ShutDown systems (ESD/PSD) involve large numbers of signals, span many process units and have strict compliance requirements. These factors increase the burden of engineering, operation and reporting, and drive the search for techniques such as Cause & Effect Matrix (CEM). By showing input signals as matrix rows and outputs as columns, CEM provides an intuitive view of shutdown trip logic and is now common practice in industry. This popularity has contributed to problems of data duplication and transcription errors when multiple incarnations of the same CEM are used at different lifecycle stages. Process engineers, programmers, operators and safety managers each view the same CEM recreated in different formats.

The authors show how the CEM paradigm can benefit from a standardised syntax and visual representation so that all the different views of a CEM are based on the same underlying data, increasing safety and productivity throughout the lifecycle.

**Keywords:** Emergency shut down, cause and effect, single-source engineering.

#### 1 Introduction

On the face of it, the design of ESD/PSD safety systems appears trivial. There are no complex control algorithms to design and test, no parameters to tune, no troublesome analog values to filter; just Boolean variables inputs setting Boolean outputs.

The Cause and Effect Matrix (CEM) visual paradigm, also known as Interlock Logic Diagrams, was introduced many years ago to capture this clear signal flow from cause to effect which is the hallmark of ESD/PSD systems. In its simplest form, it is a matrix of gridlines where named tags occupy rows and columns. A symbol placed at a row/column intersection cell indicates that a trip of that column effect will occur when that row cause is active. The simple CEM interface evolved to make room for shutdown levels, which allowed users to define a cascading shutdown hierarchy, with many degrees between PSD and ESD.

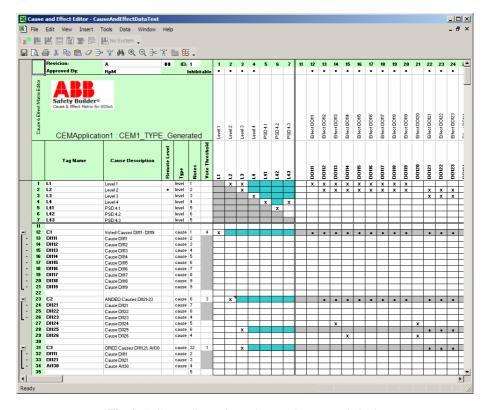

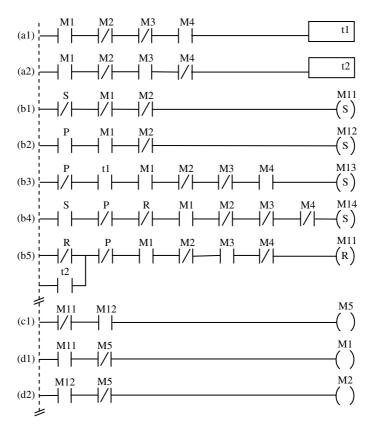

The CEM paradigm was a visual success and CEM drawings made in Excel became a de-facto standard. Some vendors followed with specialised CEM programming tools to generate control code for their respective platforms. See Figure 1 for an example of the CEM format.

|                  |                 |       |     |    |    |         | ON      | 디           | 21    | 21    | 21          | 21          |    | H<br>N      | 21            |          |           |              | 디              | 더                |   |   | 2.1            | 21               | L |

|------------------|-----------------|-------|-----|----|----|---------|---------|-------------|-------|-------|-------------|-------------|----|-------------|---------------|----------|-----------|--------------|----------------|------------------|---|---|----------------|------------------|---|

| Application Unit |                 |       |     |    |    |         | MN      | 11          | 11    | 11    | 11          | 11          |    | 11          | 11            |          |           |              | 11             | 11               |   |   | 11             | 11               |   |

|                  | Shutdown Matrix |       |     |    |    |         | ONI     |             |       |       |             |             |    | 0           | 0             |          |           |              | :              | 10               |   |   | 11             | 10               | Γ |

|                  | EXAMPLE         | logic | :   |    |    |         | A1+     |             |       |       |             |             |    | ı,          | ü             |          |           |              | ы              | ц                |   |   | ц              | п                |   |

|                  |                 |       |     |    |    |         | Alarm   | Level       | Level | Level | Level       | Level       |    | NE          | NE            |          |           |              | NE             | NE               |   |   | Q              | ND               |   |

|                  |                 |       |     |    |    |         | Type    | ESD         |       |       | BSD         | ESD         | ┪  |             | 00            |          |           | ┪            | DO<br>DO       | 00               |   |   | 00             | 00               | r |

|                  |                 |       |     |    |    |         | No Name | 1 XX-ESD1 I |       |       | 4 XX-PSD4.1 | 5 XX-PSD4.2 |    | XX-OUTPUT01 | 2 XX-OUTPUT02 |          |           |              | 6 XX-VALVE01 I | 7 XX-VALVE01-INT |   |   | 10XX-VALVE01 1 | 11XX-VALVEO1-INT |   |

| No               | Name            | Туре  | Al+ | NW | NO | Level   | -       | ··          |       |       | •           | -,          | ┪  |             | -             | $\dashv$ | $\forall$ | $\forall$    | _              |                  | Н | Н | •              | ··               | t |

| 1                | XX-ESD1         | ESD   |     | 11 | 21 |         |         | Г           | ٠     |       |             | П           | 7  | •           | П             | ╛        | ╛         | ┪            | $\neg$         |                  |   | П |                | Г                | Г |

| 2                | XX-ESD2         | ESD   |     | 11 | 21 |         |         | Г           |       | •     |             | П           | ╗  | $\neg$      | •             |          | T         | T            |                |                  |   | П |                |                  | Г |

| 3                | XX-ESD3         | ESD   |     | 11 | 21 |         | Т       | Т           |       | П     | •           | •           | 7  | ┪           | $\neg$        | ┪        | ヿ         | ╛            | $\neg$         |                  | П | П |                | Г                | Г |

| 4                | XX-PSD4.1       | ESD   |     | 11 | 21 |         |         |             |       |       |             |             |    |             |               |          |           |              | •              | •                |   |   |                |                  | Γ |

| 5                | XX-PSD4.2       | ESD   |     | 11 | 21 |         |         |             |       |       |             |             | 4  | $\dashv$    |               | _        | 4         | 4            |                |                  |   |   | •              | •                | L |

| 1                | XX-ACT-ESD1     | Alarm | IL  | 11 | 21 | XX-ESD1 |         | •           |       |       |             |             |    | •           | •             |          |           |              | •              | •                |   |   | •              | •                | Ė |

| 3                | XX-ACT-ESD2     | Alarm | IL  | 11 | 21 | XX-ESD2 |         |             | •     |       |             |             |    |             | •             |          |           |              | •              | •                |   |   | •              | •                | Ė |

| 6                | XX-INPUT01      | Alarm | IL  | 11 | 21 |         |         |             |       |       |             |             | 1  | •           |               |          | 1         | $\pm$        |                |                  |   |   |                |                  | t |

| 7                | XX-INPUT02      | Alarm | IL  | 11 | 21 |         | -       |             |       |       |             | Н           | 4  | $\dashv$    | •             | 4        | 4         | 4            | _              |                  |   |   |                |                  | ļ |

|                  |                 |       |     | L  |    |         |         |             |       |       |             |             | #  |             |               | 7        | 7         | $\downarrow$ |                |                  |   |   |                |                  | F |

| 10               | XX-ACT-VALVE01  | Alarm | IL  | 11 | 21 |         |         |             |       |       |             |             | #  |             |               |          | 1         | #            | •              | ٠                |   |   |                |                  | F |

| 12               | XX-ACT-VALVE02  | Alarm | IL  | 11 | 21 |         |         |             |       |       |             |             | 1  |             |               |          | 1         | $\pm$        |                |                  |   |   | •              | •                | t |

|                  |                 |       |     |    |    |         |         |             |       |       |             |             | _1 |             |               |          |           |              |                |                  |   |   | L              |                  | L |

| _                | XX-RESET-OUTP   |       |     | 11 | 21 |         |         |             |       |       |             |             |    | T           |               |          |           |              |                |                  |   |   |                |                  |   |

Fig. 1. Sample from a typical early CE Matrix

#### 1.1 Trends in ESD/PSD Systems

The CEM format became a popular representation but without the support of a formal standard a variety of formats proliferated, even between different lifecycle stages of the same project. Recreating the same CEM in different formats introduced delays and increased the potential for misunderstandings and errors.

The Cause and Effect Matrix paradigm had become a victim of its own success.

In addition to the proliferation of data formats and visual formats, the CEM paradigm has also been under growing pressure to cope with these important trends in industry.

- **Size and complexity:** ESD/PSD systems comprise a large and everincerasing number of tags, arranged in an increasingly complex hierarchy of cascading shutdown levels, with special cascade inhibit logic.

- Safety compliance: ESD/PSD programmable systems have high safety integrity (SIL) and the accompanying compliance burden is increasing as

regulatory demands become stricter Ref [IEC-61511]. In the operational phase, periodic proof-testing reports of the ESD/PSD are also mandatory.

- Common Control Platforms: The trend toward using commercial off-the shelf (COTS) hardware platforms and use of common control software libraries even for ESD/PSD systems with high safety integrity (SIL) requirements.

- **Decision support:** The need for operators to quickly trace backward to determine the cause(s) of a trip in an ESD/PSD system.

- Additional signal processing: ESD/PSD programmers want the freedom reconfigure the input cause signals, add additional logic before setting the outputs.

- Spanning process areas: ESD/PSD systems spans many more diverse process areas, engineered by different contractors and teams.

#### 2 Single Source Engineering

In their work with engineers responsible for large shutdown implementations, the authors discovered the benefits of "single-source engineering" (SSE) as a way of mitigating the problems created by the trends listed above. They offer the following recommendations, whose application to those problems are discussed in the following paragraphs of this paper.

- Single representation for CEM applications & visual displays: agree on a single standard visual "language" for representing CE matrices, from which the operator display and the 1131 code is co-generated.

- Single source of data for of CEM lifecycle activities: use a portable document as a single source of data for all activities throughout the lifecycle.

### 2.1 Size and Complexity

ESD/PSD systems comprise a large and ever-increasing number of tags, arranged in an increasingly complex hierarchy of cascading shutdown levels, with special cascade inhibit logic.Ref [DNV1]

The size and complexity of ESD/PSD systems have dramatically increased the effort of coding and maintaining such an application directly in one of the standard 1131 languages. A generative approach suggests itself, where 1131 code objects are automatically created based on the visual layout in the CEM diagram. The authors approve of vendors which offer such tools; programming at a higher level of abstraction is an effective way to reduce implementation errors and ease application maintenance.

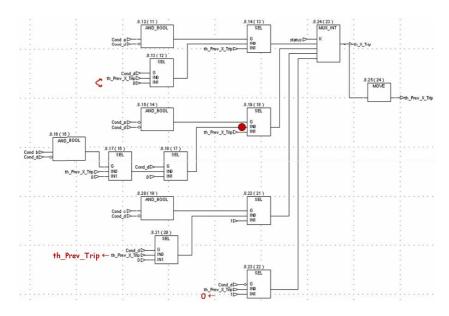

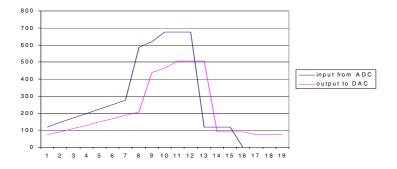

The authors tool development layout is shown in the figure below. This matrix view uses text, colour and shading patterns to show direct and indirect trips as the result of cascading level logic. These indirect effects would be difficult to trace if the logic were programmed directly in control code structured text, for example.

Generative techniques should not stop at the control code; re-creating the logic for an operator display is also a very time-consuming and error-prone task. The author's

Fig. 2. A CEM editor using colour to show cascade logic

approach is to co-generate the display by linking display artifacts with the generated code variables to provide an online view of current status.

#### 2.2 Safety Compliance

ESD/PSD programmable systems have high safety integrity (SIL) and the accompanying compliance burden is increasing as regulatory demands become stricter Ref [IEC-61511]. In the operational phase, periodic proof-testing reports of the ESD/PSD are also mandatory.

When the CEM drawing of the ESD/PSD system has become the subject of formal integrity approval by national authorities, then there is strong motivation to preserve its format throughout the engineering lifecycle. In this way, suppliers, operators and engineers have a common understanding of the CEM shutdown behaviour, based on a common visual representation. This approach assists "cognitive recognition" Ref [HCI2].

In the operational phase, periodic proof-testing reports of the ESD/PSD are also mandatory. Such reports are difficult to configure and maintain without access to the original CEM data structures from the design phase.

The solution to both of the above problems is to make the approved CEM drawing the single source of engineering data for all engineering and operational activities

When the document is approved then it can be argued that all subsequent transformations based on that document also inherit this approval. In the authors tool development, a single document serves as the basis for all lifecycle activities, including the operator display. This document can then be input to an editor/compiler capable of generating IEC-61131 compliant control code objects Ref [IEC-61131] and the operator display.

The advantages of having a "single source of truth" are many (Refs [CE1], [CE2]), and these assume an even greater importance for the development of safety-critical systems. The authors suggest that this principle should be encouraged in future drafts of both corporate and international safety standards.

Using a single document throughout the engineering process and then taking this same document into the daily operational phase of a system will reduce synchronisation problems. Version checking and inconsistency reporting between the original documentation and the online operator display: By generating the control logic from the master document, a version number can be introduced to the control logic and later used online to check that the operator display has the same version number as the code running in the controller. This will help to ensure that the operator display is always up to date with the control logic: the display matches the plant "as built".

A single source approach enables printing of online status in a format that is identical to the design documentation: This aids the task of tracing trip signals and documenting shutdown situations in a consistent way. It is also very useful to be able to include information like versions, build numbers, approvals and engineering and operator notes in the online display.

#### 2.3 Common Control Platforms

There is an industry-wide trend trend toward using commercial off-the shelf (COTS) hardware platforms and the use of common control software libraries even for ESD/PSD systems with high safety integrity (SIL) requirements. This trend will soon extend to safety fieldbusses [CE1].

This trend means that modern safety solutions must conform to standard languages, interoperate with standard device control software libraries and standard operator displays. Most importantly, it means that ESD/PSD safety systems can no longer assume exclusive ownership of the devices and must accommodate a wider and "wilder" range of configurations. The downside of this trend has the potential to make the engineering and operation of ESD/PSD systems more difficult and potentially increase the chances of design errors.

The benefits of using a single platform for safety and non-safety applications can be realised if the critical parts of that platform are safety certified. For control software this means selecting a relevant subset of 1131 function blocks or control-modules and ensuring that these are SIL-compliant. This subset should be sufficient to cover the needs of ESD/PSD programming. These safety status of these types should be clearly visible within the programming tool and that tool's compiler should check that their usage is consistent with the safety level of the entire application and the

target controller. This approach allows safety engineering to flow together with the basic process control system engineering.

Implicit in this recommendation is the use of pre-defined 1131 types or classes, stored in tested and approved libraries. This type-based approach is especially important for safety programming, whether it is manual or generative, since it builds on approved and version-controlled code.

The benefits of standardisation can be extended by encapsulating all the variety of device types (transmitters, valves, motors etc.) inside control object types which expose their internal states in a standard way, for example in a bit pattern of a defined 32-bit variable. Ref [PCCUG]

#### 2.4 Decision Support

As the complexity of ESD/PSD systems has increased, so has the need to assist operators in quickly tracing backward to determine the cause(s) of a trip, without having to deduce the cause from many different documents and inputs Ref: [HCI]. Operators find it increasingly difficult to understand a trip situation and trace backward to the originating causes in real-time.

The solution to this problem is to provide the operators with online displays which allow him/her to see the online status of the ESD/PSD system at any level of aggregation, with the freedom to drill down to individual process areas or devices. At the lowest device level, the operator is presented with an online "faceplate" display showing the device signal pathway traced back to one or more input devices.

To achieve this desirable functionality requires that all the signal pathways from output backward to input must be charted and embedded in the operator display logic. Typically this signal flow information is hidden within the temporary data structures of the 1131 code compiler and is not available to any other engineering tools.

The authors found that the most robust way to re-create this path information was to adopt the approach pioneered by a team led by Alan Munns of ABB in the UK, called the Priority Command Concept (PCC). The PCC is an open concept for 1131 type design. To be PCC-compliant, a control type (or "class") must expose its instance name and its internal state in data elements NAME and ACTION, respectively. A further requirement is that each PCC type must propagate the name of the PCC instances to which it is connected, both up- and down-stream. This propagation is done via 1131 string operations performed once in the first scan after start-up in the controller.

Each PCC instance knows its neighbors: this allows operator viewer tools to trace the signal pathway from output to input device, regardless of the number of intermediate control objects. These tools can automatically create a dynamic visual display element which is inserted into the view of the output device (See Figure below).

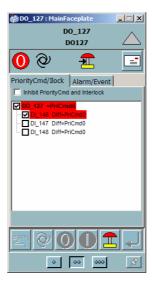

The operator can access any of the devices participating in the CEM matrix by right-clicking on the display itself and choosing the "faceplate" item as shown in the following figure.

Fig. 3. Operator output signal faceplate showing signal pathway from input

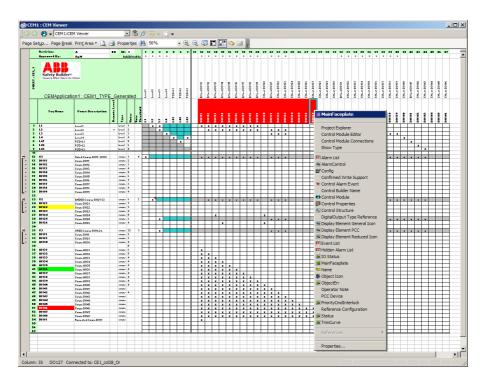

Fig. 4. CEM display for operator showing quick access to signal object

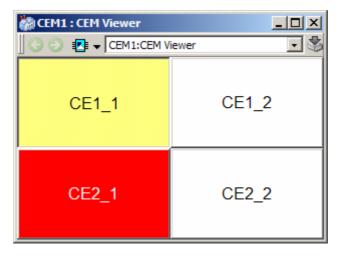

At the highest level, the user can navigate between the various process areas represented as different parts of the CEM matrix. The navigation display (shown in the figure below) shows these areas to the operator and are color-coded with the current status of all their contained device signals. The operator can click on the area "button" and be presented with the CEM matrix for that area, as shown in the previous figure.

Fig. 5. Operator's top-level CEM Navigation display

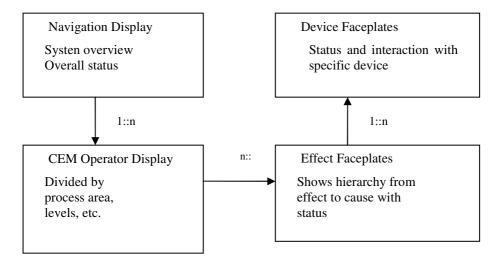

The relationships between the various displays are shown in the following Figure.

Fig. 6. Relationships between operator CEM displays

#### 2.5 Additional Signal Processing

ESD/PSD programmers want the freedom re-configure the input cause signals, add additional logic before setting the outputs. The previously clean and simple CEM grid format sprouted many footnotes and comments as designers struggled to capture special logic cases on the crowded matrix grid. An additional problem is the quality of the generated code, which in most cases is custom IEC-61511 structured text.

The solution to this problem is three-fold: firstly, vendors and industry should agree on a set of functionality which satisfies the needs of most CEM engineers. In particular, voting arrangements should be a standard part of such a proposed CEM language. The authors propose that the CEM language syntax be limited to these basic functions:

- Signal Name & Description

- Trip ("X")

- Inversion

- Normal & Cascade Inhibit

- Reset

- Time Delay

- Voting (NooM)

- Comments

Secondly, analog thresholding, boolean latching and other related configuration work should be encapsulated in the signal device object, so that the CEM is freed to do what it does best: show the routing cleanly and intuitively.

Custom textual coding nullifies one of the main benefits of single source engineering. So the final recommendation here is to use a control library in which even simple "routing" operations such as AND / OR / SPLIT are SIL- marked object types. These can be configured safely by the CEM editor user and then instantiated by the CEM editor's generation function, thus ensuring higher quality executable code. In the approach taken by the authors, these control object types simply route the originating device data, packaged within a standardised bit pattern of a 32-bit variable data element. This data type contains a data word (ACTION) with a standard bit pattern for commanded action, inhibit, connected and a few other states. The simple routing object type instances operate on this data.

#### 2.6 Spanning Process Areas

ESD/PSD systems span many more diverse process areas, engineered by different contractors and teams.

Single source engineering is challenging in a multi-disciplinary and geographically dispersed engineering environment. Vendors who claim to support this principle offer centralised database or object stores, but access to these are complicated by the need for special client software and the ability to cross corporate firewalls.

The authors believe that the internet points the way to a more flexible architecture based on exchange of a document in a standard format which contains its own validation logic. This validation could be either in the form of an XML schema or via a component (such as ActiveX) which is embedded in the document. Such a document is highly portable: it can be exchanged via email between all the partners in

a large project, without difficulties caused by firewalls, licensing, and installation and setting up special access permissions.

A typical use case illustrating this solution is when a contractor can specify CEM connections in a portable document without being forces to install any special software by the control system supplier. He/She then sends the document via email to the control system supplier who can then automatically generate the control code and the operator display without modifying or translating the original CEM document.

Finally, automation vendors are urged to now agree on a common visual and textual representation which should be submitted to a standards-setting body for approval. Taken together, these are syntax rules for a proposed common CEM "language". The textual representation should be in the form of an XML schema. The accompanying visual standard should reflect the contents of the XML representation in a universally recognisable way, which is intelligible to CEM programmers and operators.

#### 3 Conclusion

Let us conclude by marking up our original list of problems with the recommendations:

- **Size and Complexity:** ESD/PSD systems comprise a large and everince increasing number of tags, arranged in an increasingly complex hierarchy of cascading shutdown levels, with special cascade inhibit logic.

- o Program directly in the CEM matrix and use tools to generate both the control code and the operator graphic displays.

- Safety Compliance: ESD/PSD programmable systems have high safety integrity (SIL) and the accompanying compliance burden is increasing as regulatory demands become stricter Ref [IEC-61511]. In the operational phase, periodic proof-testing reports of the ESD/PSD are also mandatory.

- o Use a single CEM data source for lifecycle compliance activities.

- Common Control Platforms: The trend toward using commercial off-the sheflf (COTS) hardware platforms and use of common control software libraries even for ESD/PSD systems with high safety integrity (SIL) requirements.

- Use a single common library with a subset of SIL-approved types which share a common interface with other types.

- **Decision Support:** The need for operators to quickly trace backward to determine the cause(s) of a trip in an ESD/PSD system.

- Use object types which support upstream signal tracing and tools which can generate displays showing the active device signal pathways.

- Additional Signal Processing: ESD/PSD programmers want the freedom re-configure the input cause signals, add additional logic before setting the outputs.

- Use an approach which allows reconfiguration and additional routing logic based on types, not loose code.

- **Spanning Process Areas:** ESD/PSD systems spans many more diverse process areas, engineered by different contractors and teams.

- O Use a portable document which can be easily shared amongst project teams.

- O Use a single visual representation "language"; make it a standard for programming by providing tools to generate the required 1131 code objects.

#### Acknowledgements

- Alan Munns, ABB UK, leader of the PCDeviceLib (PCC) development team, for his permission to cover the benefits of PCDeviceLib concepts in this paper.

- Steinar Engh, ABB Norway, for his valuable feedback as an experienced cause and effect matrix designer and user.

#### References

- [IEC-61511] International Standard IEC-61511 Functional safety –Safety instrumented systems for the process industry sector, International Electrotechnical Commission Geneva, Switzerland 2003

- [IEC-61131] International Standard IEC-61131 Programmable controllers, International Electrotechnical Commission Geneva . Switzerland 2003

- [PCCUG] PCDeviceLib User Documentation , ABB document # 3BGB001947D0063, ABB 2004 .

- [CE1] Control Engineering Magazine "Safety Networks", 1/12/2004

- [DNV1] Offshore Standard DNV-OS-A101, "Safety Principles and Arrangements", 2001, Det Norske Veritas (DNV).

- [HCI1] Carroll, JM; Human Computer Interaction in the New Millenium", Addison Wesley, New York, 2001

- [HCI2] Preece, J; Human Computer Interaction", Addison Wesley, New York, 1999

- [CE1] Control Engineering, Sept. 2003, "Maintaining a Single Source of Truth."

- [CE2] ARC Insight Oct 2004, "Leverage Engineering & Design Information to Improve Plant Performance"

## Combining Extended UML Models and Formal Methods to Analyze Real-Time Systems

Nawal Addouche<sup>1</sup>, Christian Antoine<sup>2</sup>, and Jacky Montmain<sup>2</sup>

<sup>1</sup> Ecole des mines d'Alès, Parc Scientifique Georges Besse, 30035 Nîmes, France nawal.addouche@ema.fr <sup>2</sup> URC CEA-EMA, Parc Scientifique Georges Besse, 30035 Nîmes, France {christian.antoine, jacky.montmain}@ema.fr

Abstract. In the paper, we present a methodology developed in order to verify probabilistic temporal properties related to dependability of real-time systems. The methodology is made of three essential steps. The first one is a UML profile called DAMRTS (Dependability Analysis Models for Real-Time Systems) designed using GME tool. The aim is to model a real-time system with qualitative and quantitative information related to its quality of service. In this profile, UML statecharts are used to represent the system behavior. An extension is introduced with probabilities, real-time requirements and nondeterministic choices. The second one proposes a translation from the extended UML statecharts to probabilistic timed automata (PTAs). In this step, global clocks are used to represent synchronization of concurrent UML statecharts in probabilistic timed automata. The last one concerns a probabilistic model checking with PRISM tool. This requires specification of dependability properties with a suitable temporal logic.

#### 1 Introduction

Several approaches have already been explored to introduce quantitative information in the dynamic UML models. A stochastic extension of UML statechart diagrams is proposed in [7]. It is based on a set of stochastic clocks which can be used as guards for transitions. The clock value is given by a random variable with specified distribution function. Other approaches are also proposed to formalize UML models which are extended with quantitative information. Dynamic UML models are formalised with stochastic Petri nets in [15], with stochastic process algebra in [5] or with continuous time Markov Chains such as we proposed it in [2]. This one is adequate for the performance evaluation and the verification of some dependability properties. However, the formal model contains only rates. Then, it is not suitable for modeling real-time systems. Different models exist to describe real-time systems such as timed automata [3] which have a clear semantics and for which a tool support for automatic verification (Uppaal, Kronos) is available.

The Unified Modeling Language (UML) [16] which becomes an official standard of the Object Management Group (OMG) is widely adopted in industry. This semi-

formal language, easy-understood and well-established design notation in the software engineering community, is extended to support the aspect-oriented design for a system. UML support many application domains and provides a common notation independent of the kind of systems that are developed.

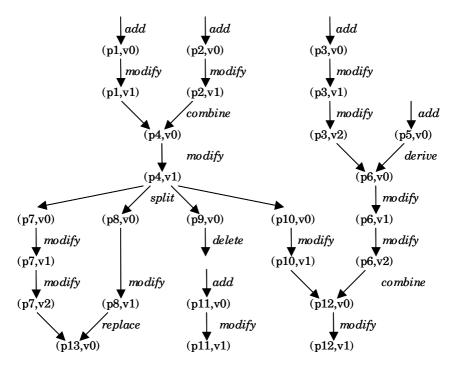

To combine the advantages of intuitive modeling by UML with formal verification, we chose the approach which consists to transform UML models into the input language of an existing model checker. Input of a model checker is a formal description of a system. For formal analysis, it is necessary to define what kind of semantic requirements are implied by the domain and what kind of semantics that easily allows translation into the formal model to be analyzed by the model checker. Our contribution includes:

- Definition of the profile DAMRTS [1] for modeling and analyzing real-time systems: a class diagram is proposed to represent static model with quality of service of system components; the conventional UML statecharts are extended with probabilities and real-time requirements,

- Specification of the nondeterminism in extended statecharts and synchronization of concurrent statecharts,

- Métamodeling with the Generic modeling Environment (GME) to construct the proposed profile,

- Translation of extended UML statecharts to probabilistic timed automata: global clocks are defined to represent synchronization of UML statecharts.

In section 2, the methodology of real-time systems analysis is described. The dynamic view of UML models is presented in sections 3 and 4. We present in section 5, real-time constraints of an assembly chain as well as their behavioral UML models as defined in the profile DAMRTS. This one is designed using GME tool as presented in section 6. The behavioral UML models are nondeterministic, with probabilistic transitions and real-time aspects. That make possible to translate them into probabilistic timed automata as given in section 7. The translation process of resulting models is also described in this section. In section 8, we give an overview on the type of properties that can be checked. We conclude with section 9.

## 2 General Methodology

In order to have UML accepted by the real-time development community, the OMG group has proposed a profile called "Schedulability, Performance and Time" [17] for real-time systems. In this profile, some supports are introduced in UML to capture a maximum of real-time requirements and to perform the real-time development tasks directly on UML models. Beside the usual analysis and design stages, scheduling analysis, performance evaluation and formal verification of critical properties are included. However, the two last activities are partially covered because "quality of service" requirements are introduced without a clear indication about the formal verification of this type of properties. Adapted tools to formal verification or performance evaluation on these UML models are not yet available.

For the reasons indicated above, a new profile called DAMRTS is proposed to analyze and verify dependability properties of real-time systems [1]. It represents an

extension to the reference metamodels of the OMG profile "Schedulability, Performance and Time" [17]. The first aim is to be compliant with the standard OMG profile. The second one is to provide concepts that enable to specify a real-time system with its real-time constraints and probabilistic information. A behavioral UML models are proposed with a formal semantics served to probabilistic model checking [10]. It is developed with probabilities and real-time aspects, resulting in probabilistic timed automata as semantics models. These models are used to verify probabilistic temporal properties related to the dependability of real-time systems.

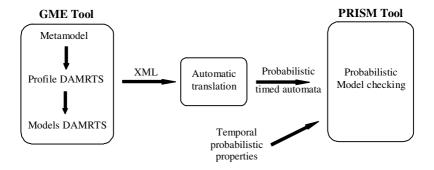

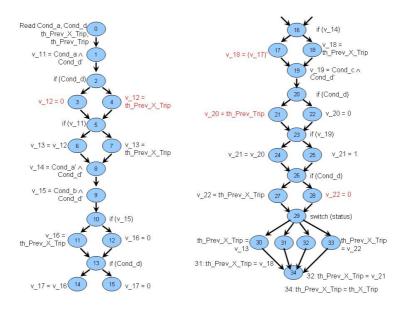

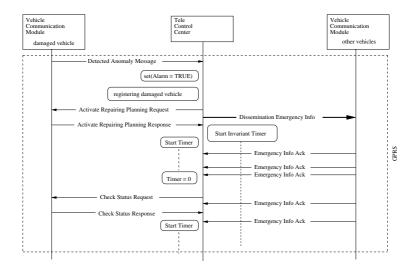

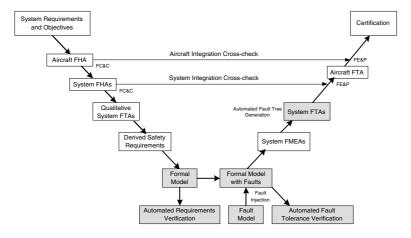

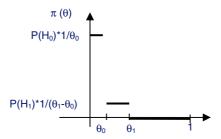

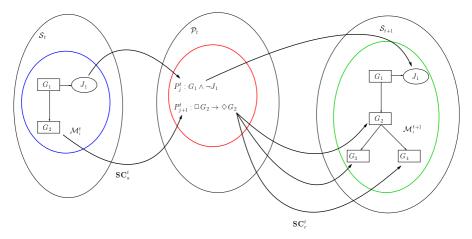

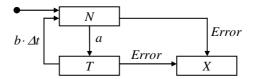

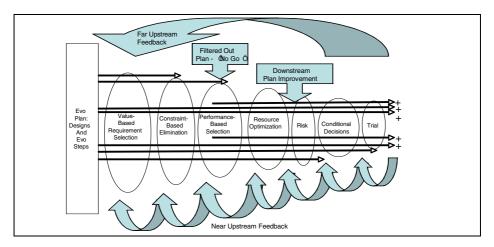

**Fig. 1.** Global methodology

As depicted in fig.1, the proposed approach is presented with the essential steps that allow associating a formal method to UML models extended with probabilities and time. The GME tool is used to construct metamodels specifying the modeling paradigm (modeling language) of our application domain. The modeling paradigm contains all syntactic, semantic and presentation information regarding the domain of real-time systems dependability. This is developed in section 6.

Once the profile DAMRTS is built, we model the real-time system. The output of GME tool is a file having an extended XML format. The DAMRTS models are then exported in XML format for which an automatic translation is applied to transform UML behavioral models into probabilistic timed automata as it is detailed in section 7.3. The PRISM tool is then used to verify the properties of real-time system.

## 3 Modeling with Extended UML

To represent dynamic aspects of the system, extended UML statecharts and collaboration diagrams are used. Combination of these two diagrams allows representing all system interactions. Indeed, the collaboration model describes external interactions between objects whereas UML statecharts diagrams represent how an instance of a class reacts to an event occurrence.

A collaboration diagram consists of objects and associations that describe how the objects communicate. It represents the structural organisation of objects which ex-

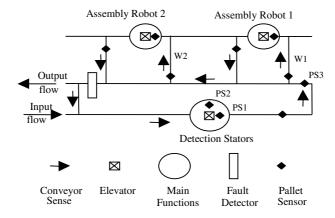

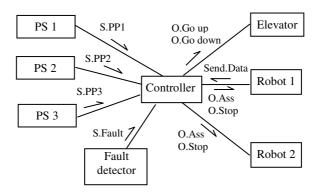

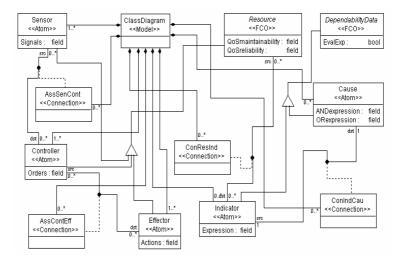

changes messages. In the DAMRTS profile, the signals and the orders are the two types of messages taken into account. The first ones are sent from objects of Sensor classes to objects of Controller class. The second ones are sent from instances of Controller class to instances of Effector classes (see fig 3).

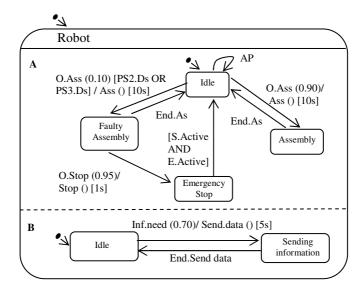

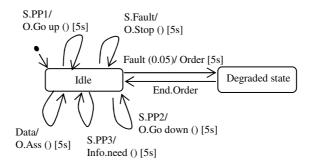

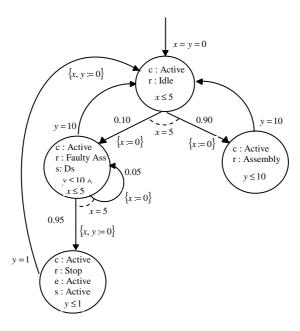

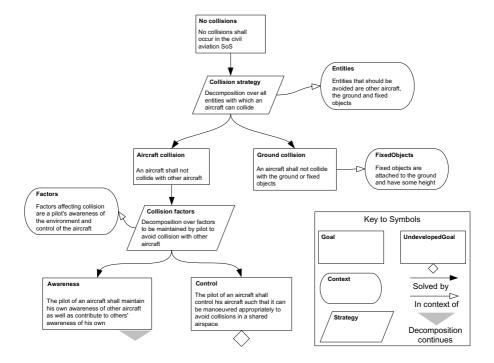

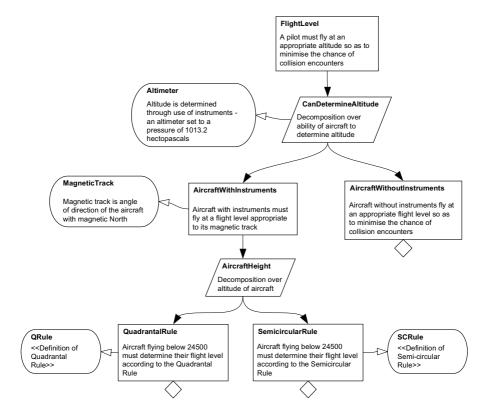

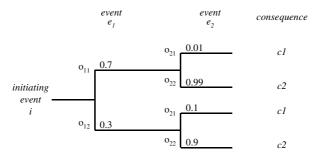

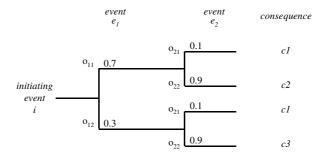

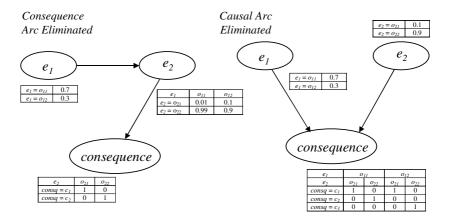

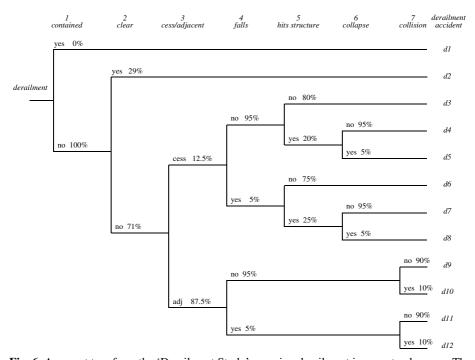

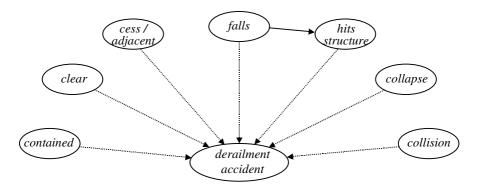

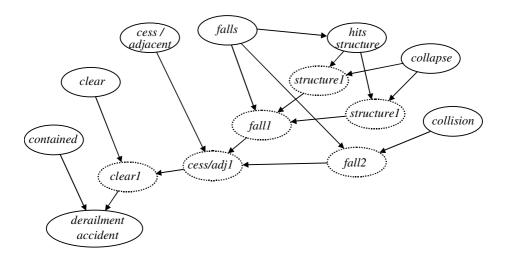

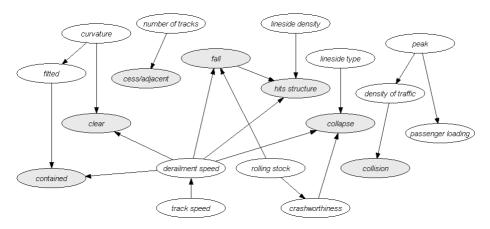

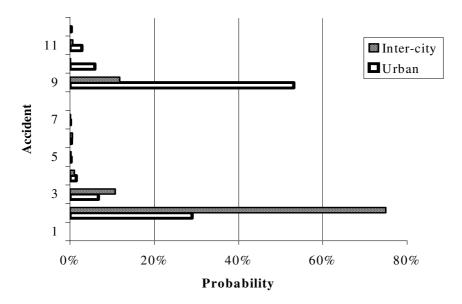

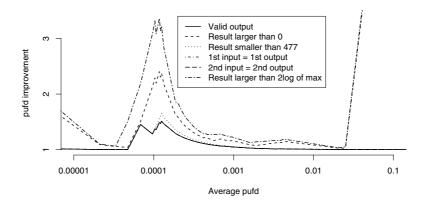

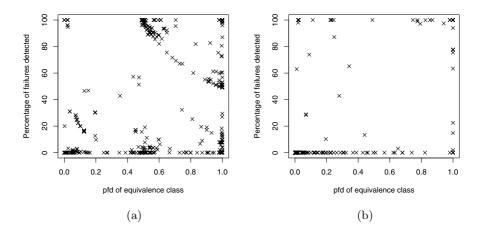

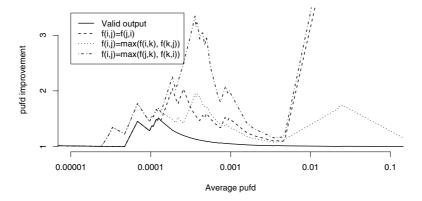

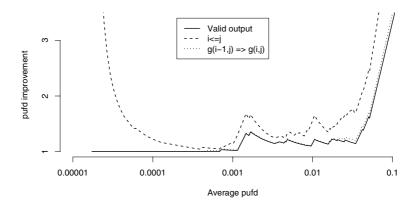

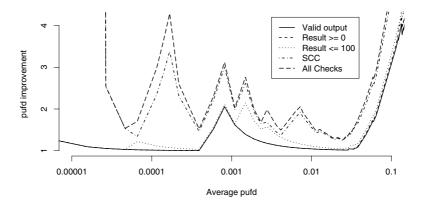

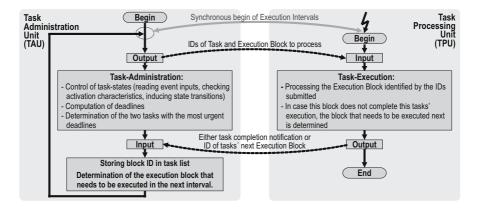

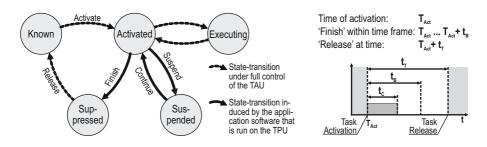

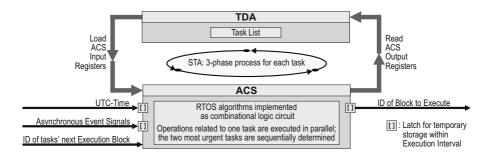

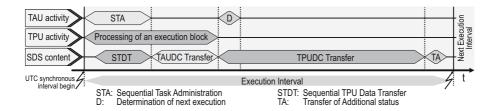

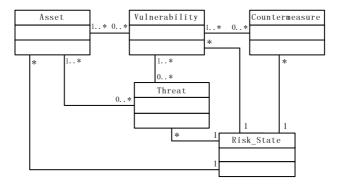

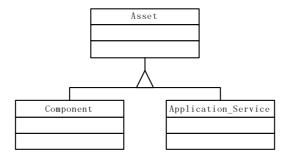

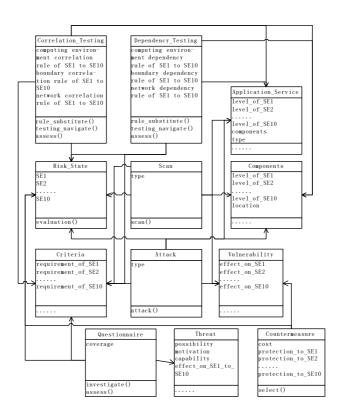

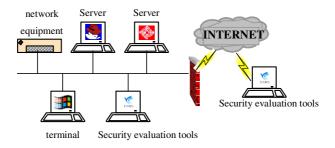

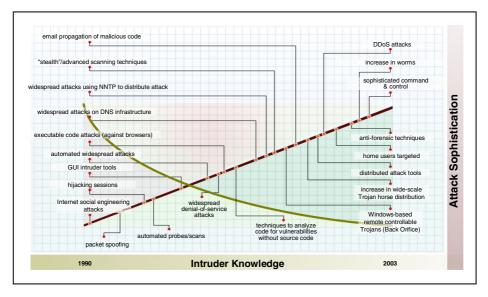

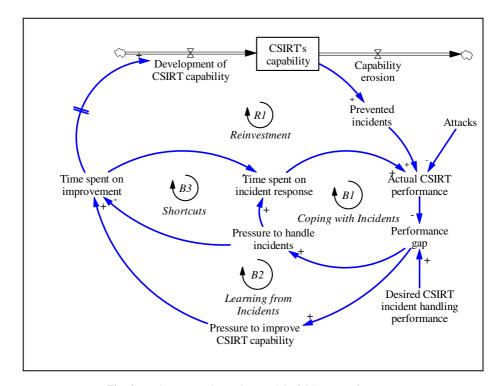

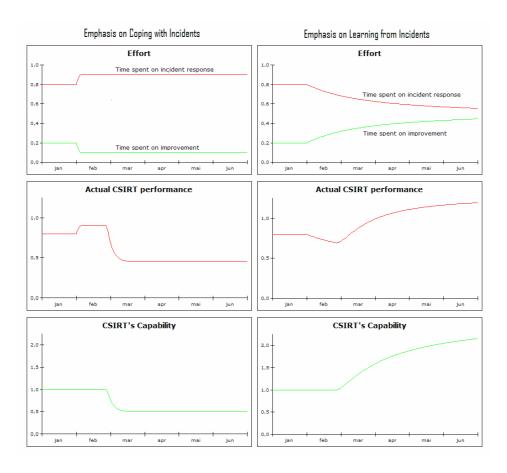

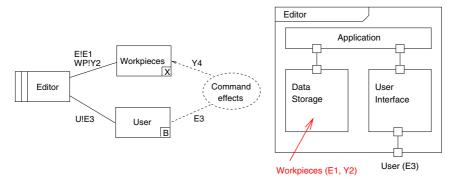

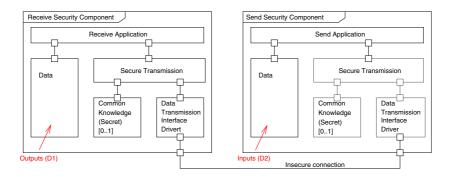

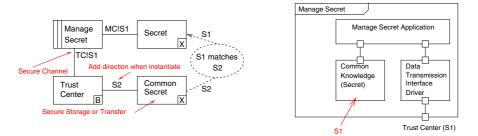

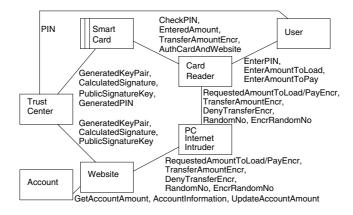

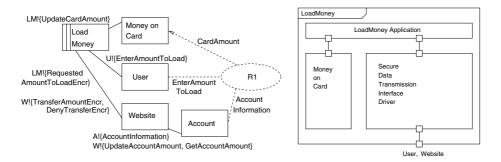

The proposed statecharts allow expressing events with probabilities and actions with real-time constraints. The nondeterminism and synchronization are defined as follows: